如何写好Verilog代码

1、首先,使用Verilog语言进行开发时,要了解语句的可综合性。

即哪些语句在实际使用中,可以综合成硬件电路,进而实现功能。

不可综合的语句有:

time,defparam,$finish,fork,join,initial,delays,UDP,wait

其中,initial语句常用于testbench的编写,但其为不可综合语句。

2、其次,对于可综合语句,每种语句的执行效率均不一样。

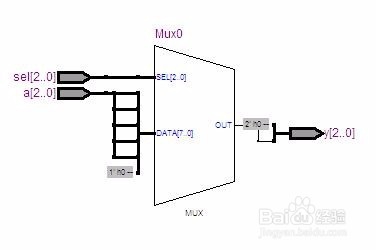

举例说明,对于一个case语句,综合器将每个分支均综合为一段电路,通过数据选择器将结果输出,其结果为并行的,无优先级;而对于if语句,实现相同的功能,综合器综合出的电路为一整片组合逻辑电路,有明确的优先级。

对于常见的同步电路设计,if语句则应尽量使用case语句代替;

3、最后,给出一些Verilog语言编写的建议,供各位参考理解。

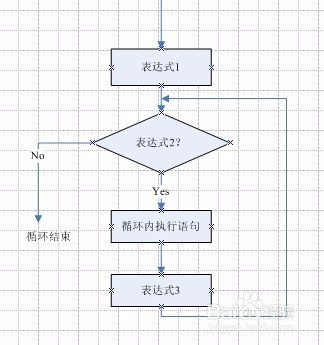

1. 避免使用高层级的循环结构;

由于for语句的综合是按照循环层数实现的,即有N层循环,综合器会综合出N个电路,以完成for循环,所以在设计中,for循环也应尽量避免。

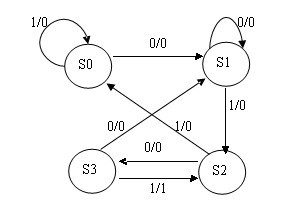

4、2.对于规模较大的代码使用case状态机

3.避免使用if-then-esle状态语句

4.不要使用非DCM或PLL产生的内部时钟

5.在设计中,尽量减少时钟数量

5、6.确保程序内部创建的复位信号都是同步的

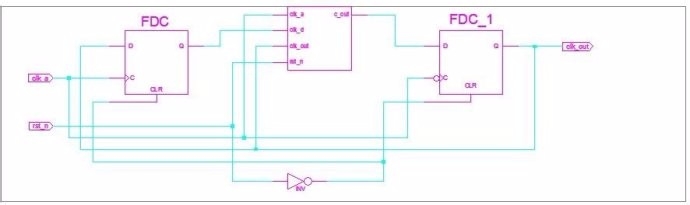

7.只使用时钟信号的单边沿

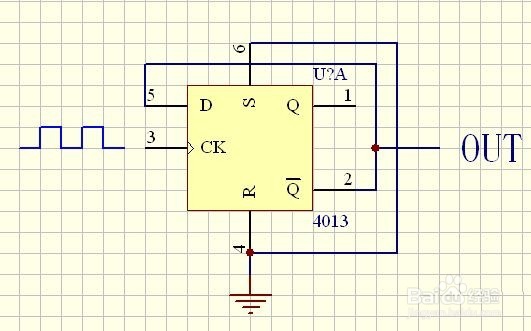

8.尽量避免锁存器,使用边沿触发器

9.通过同步电路来切换时钟域

声明:本网站引用、摘录或转载内容仅供网站访问者交流或参考,不代表本站立场,如存在版权或非法内容,请联系站长删除,联系邮箱:site.kefu@qq.com。

阅读量:102

阅读量:73

阅读量:43

阅读量:171

阅读量:158