EtherCAT主站开发经验——基于Zynq

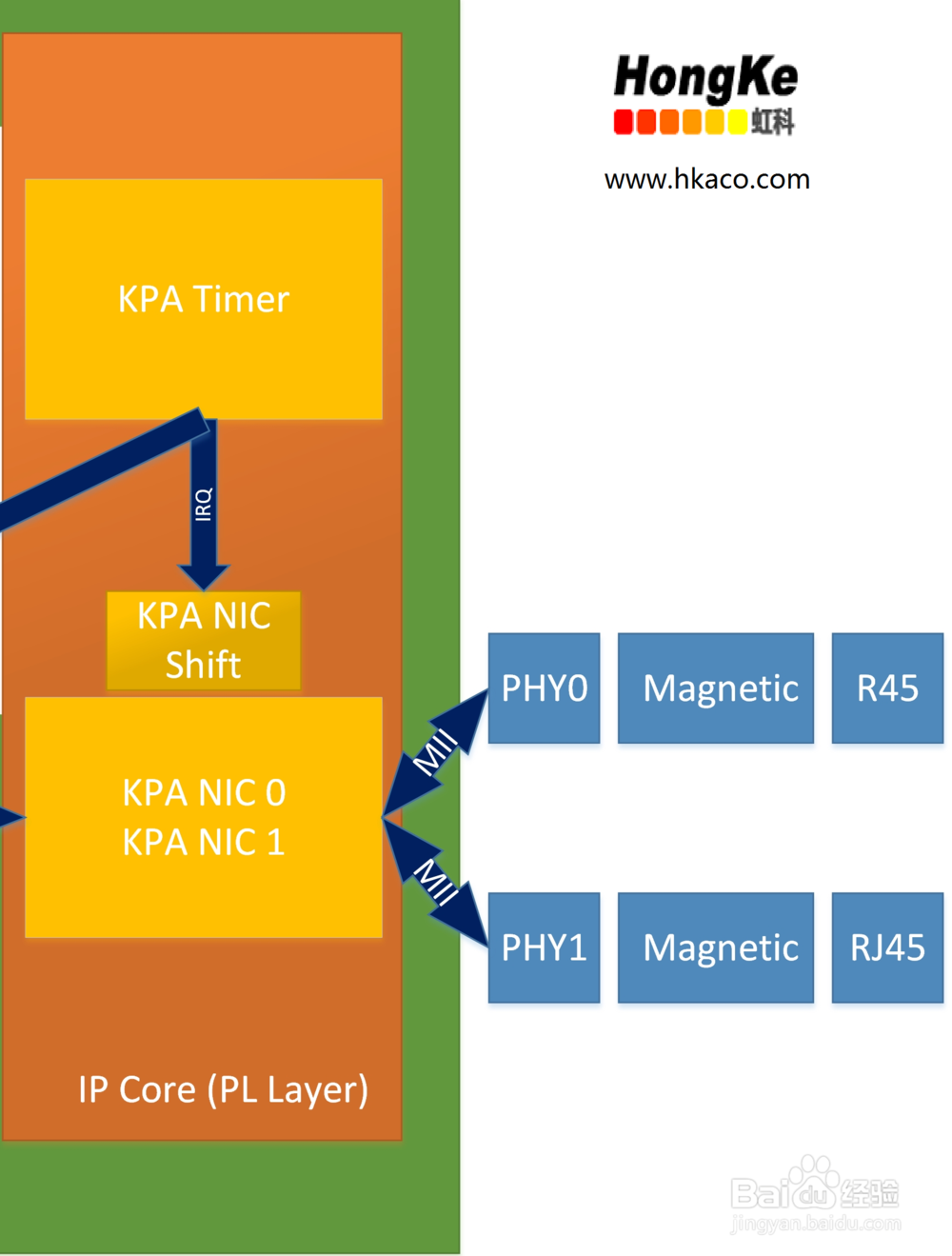

1、整个方案的结构框架

2、PS层,即Zynq中的ARM处理器部分,加载了Xenomai/Rt-Preempt实时操作系统和KPA的EtherCAT主站源代码(EtherCAT Master Core)。Xenomai实时操作系统让整个通讯过程达到了us级别,而KPA的EtherCAT的主站源代码负责按照EtherCAT机制处理数据并打包给KPA NIC Driver(网卡驱动),KPA NIC Driver把打包好的数据通过AXI总线传给PL层中的IP core。

3、PL层,即Zynq中的FPGA硬件部分,加载了KPA的主站IPcore,该IPcore使用logic构建了两个NIC(MAC)+Timer,并封装在一起。KPA NIC 0/1通过AXI总线接收来自KPA NIC Driver的数据,并对数据进行重新排列,最终给到PHY,再通过变压器,RJ45把EtherCAT数据帧发出。KPA Timer提供时钟源用于同步KPA NIC Driver和KPA NIC 0/1,而如果设定了Shift Sending Frame时间(KPA主站IPcore特有的),那么KPA NIC Shift会对NIC发出数据的时间进行延迟,从而使得网卡发出数据帧的时间在最大抖动时间之后,以确保从出站网口发出的数据帧是精确定时的,并且包含完整的数据信息。一般选取从站响应时间的平均数作为参考的Shift Sending frame。

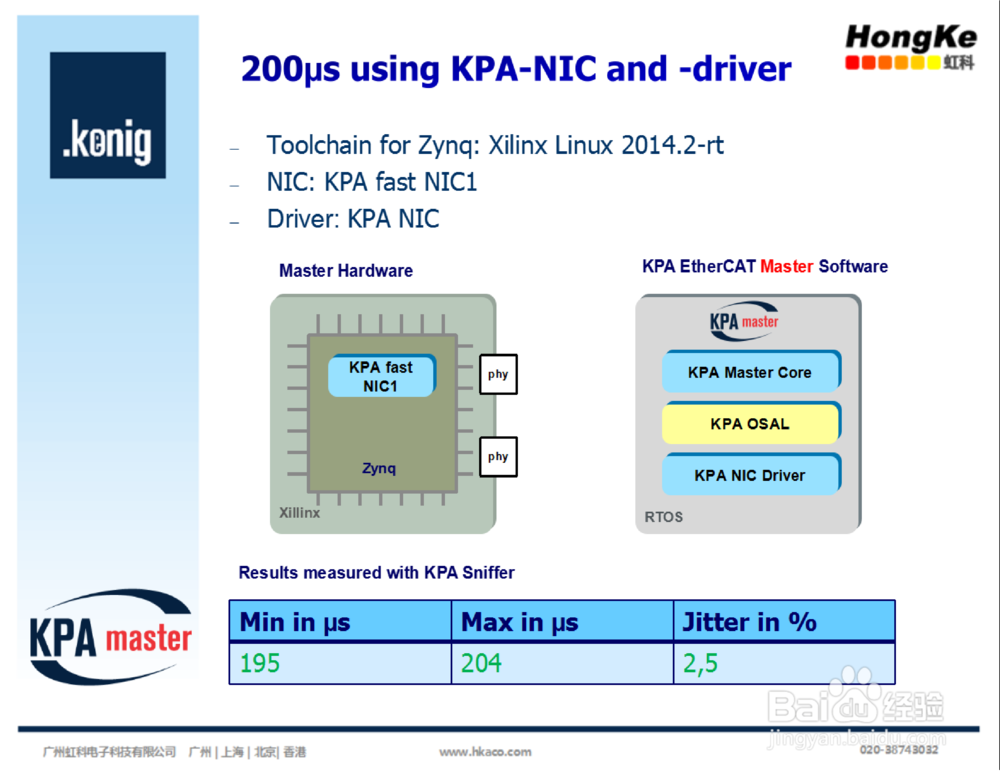

4、KPA NIC Driver和KPA NIC 0/1的作用对于整个EtherCAT主站的性能稳定性有着决定性的作用,从下面两幅图可以明显地看到,使用标准的NIC Driver和Zynq NIC时抖动超过了100%,而使用KPA NIC Driver和KPA NIC时抖动只有2.5%。由此可见,KPA对于网卡的驱动和NIC的优化使得Zynq运行EtherCAT主站时更加地稳定可靠。

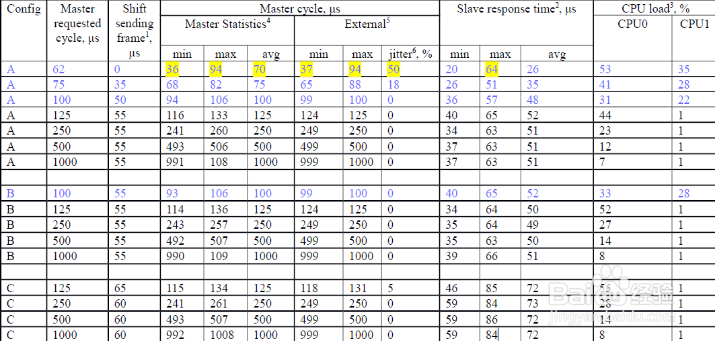

5、下面再来看一组测试结果,采用的是Xilinx Zynq™-7000+Xenomai,运行时间为60分钟。共三组配置:

Configuration A: 2 slaves, no DC, no Mailbox, cyclic frame 60 bytes

Configuration B: 2 slaves, DC, no Mailbox, cyclic frame 60 bytes

Configuration C: 16 slaves (axis), 192 Bytes of Process Data, DC, cyclic frame 266 Bytes

解释:

第一行A:master requested cycle=62

因为从站的响应时间几乎接近主站的周期时间,所以可能导致上次的数据帧未返回,就要准备下次的数据发送,加上本身的系统时钟抖动,从而引发了更大的外部总线定时不稳。此类情况建议增大主站周期。

第三行A:master requested cycle=100

CPU负载31%即需要大概31微秒,从站最大响应时间57微秒。所以此时设置的主站周期时间就合理了,通过设置Shift sending time,正真从主站端口发出的数据帧几乎没有了抖动。

6、总结:采用Zynq的方案开发实施的EtherCAT主站有着更强大的处理能力和响应速度,同时减少主站自身的抖动,但开发难度相对较大。