C6678+Kintex-7 CameraLink实时检测与处理系统

1、Kintex-7产品系列FPGA基本参数如下图所示:

1、C6678的资源框图如下图所示:

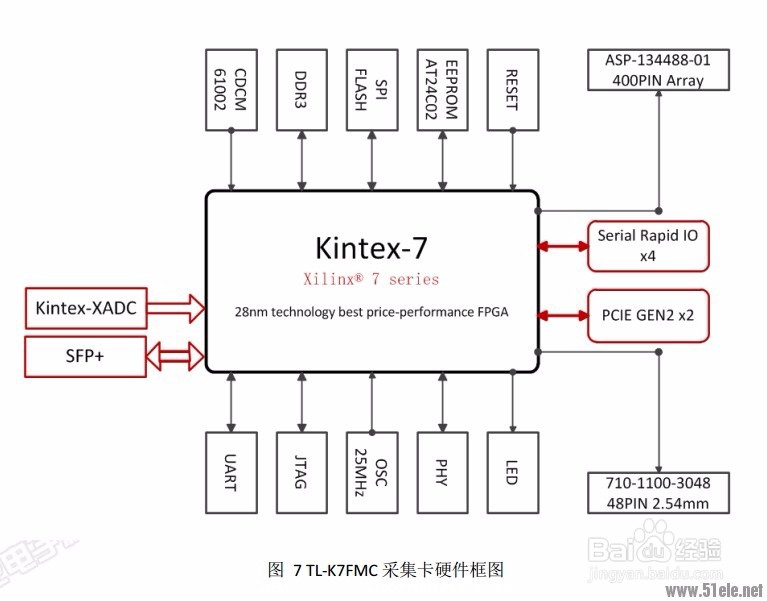

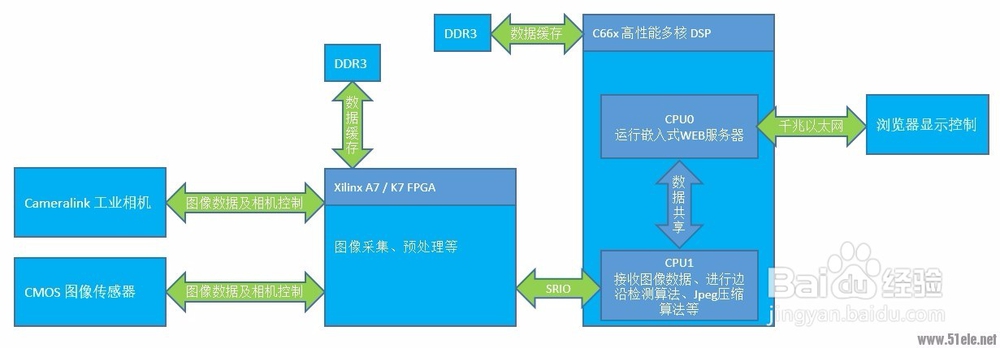

1、基于Xilinx 7系列FPGA+TI C66x多核DSP的高性能图像处理演示DEMO整体框架如下图所示。

2、示例程序主要演示了FPGA对Cameralink工业相机数据的采集,FPGA与DSP的高速通讯,以及多核DSP如何协同工作。

首先FPGA采集Cameralink工业相机输出的图像数据并缓存至本地缓存中,当缓存一帧完整的图像后,通过高速RapidIO接口把图像数据传送至DSP的内存中,传送完1帧图像后向DSP发送中断以通知DSP处理数据。

然后多核DSP会把该中断路由至Core1,Core1接收到中断后对原始图像进行边沿检测算法,然后将原始图像和通过边沿检测后的图像并成一副图像,并调用JPEG压缩算法将生成后的图像压缩为JPEG格式。JPEG压缩完成后,会将JPEG格式的图像数据复到Core0与Core1共的内存中,并且Core1会向Core0发送IPC中断,通知Core0处理数据。

最后多核DSP使用Core0内建嵌入式WEB服务器,PC机通过浏览器即可方便的查看JPEG格式的原始图像和经过算法处理的图像。

1、程序运行后通过浏览器看到的效果如下图所示:

2、本次运算,使用的FPGA是Xilinx Artix-7,使用的DSP是双核的C6657,C6657的两个核心都运行在1GHz,FPGA与DSP之前通过RapidIO传输数据。FPGA发送到DSP的图像数据是640*480 = 300KB,边沿检测后的图像是640*480 = 300KB,然后把这两副图像生成为1280*480 = 600KB的一副图像,然后把生成后的图像压缩成JPEG格式,大概在100~300K之间。

经过运算,每秒钟的图像在31帧时 Core0 的使用率为5%左右,Core1的使用率为55% 左右。当然,这是没有经过任何优化的性能,如果对程序加以优化,性能将会有大幅度的提升。优化可以从多方面入手,比如可以打开CCS编译器的优化选项让编译器自动优化,或者人工优化代码,许多指令经过优化后可以并行执行,这样就可以使CPU在相同的时间执行更多的指令,从而提高CPU的效率。测试程序中图像的处理是使用CPU来完成的,我们可以使用EDMA3来完成这些工作,可以在很大程度上减少对CPU资源的占用,从而提高CPU的效率。另外,如果使用的是8核心的C6678,那么就可以把算法分配到更多的核中执行,性能将会成倍的提高。

依据TI官方的数据,C6678在默认cache配置下(即L1D cache:32KB,L1P cache:32KB,L2 cache:128KB),如果C6678运行在1000MHz,那么JPEG压缩的性能是:66.66 Mega pixels/second【1】,可见其数据处理能力是非常强大的。

1、该系统由于采用高性能处理器,系统设计框架经典实用,用户可以在该框架中,很方便的添加自己的应用。对采集的图像数据进行一系类复杂的算法处理,而且实时性非常好,易于移植至工业检测,机器视觉,目标追踪等诸多领域。