数字钟电路设计与Multisim仿真

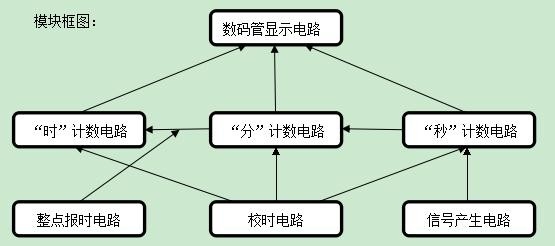

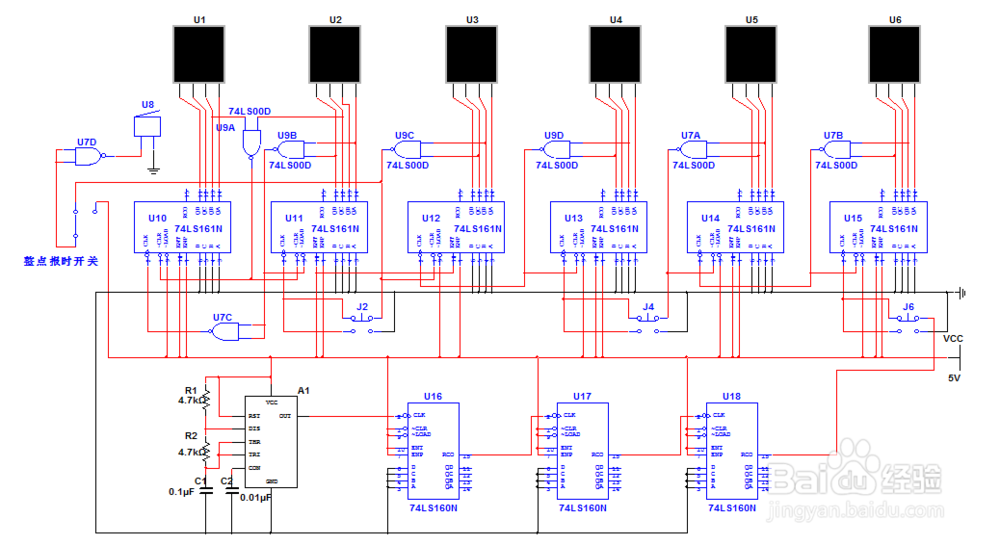

1、设计方案:利用555产生1kHz的时钟信号,再利用三个74LS160串联进行分频,产生1Hz的时钟信号,并将其导入用74LS161和与非门设计的00-59的循环计数电路(即数字钟的“秒”计数电路)中,然后依次是“分”计数电路和“时”计数电路,同时用数码管显示出来。最后,再在这基础上添加整点报时和校时功能。

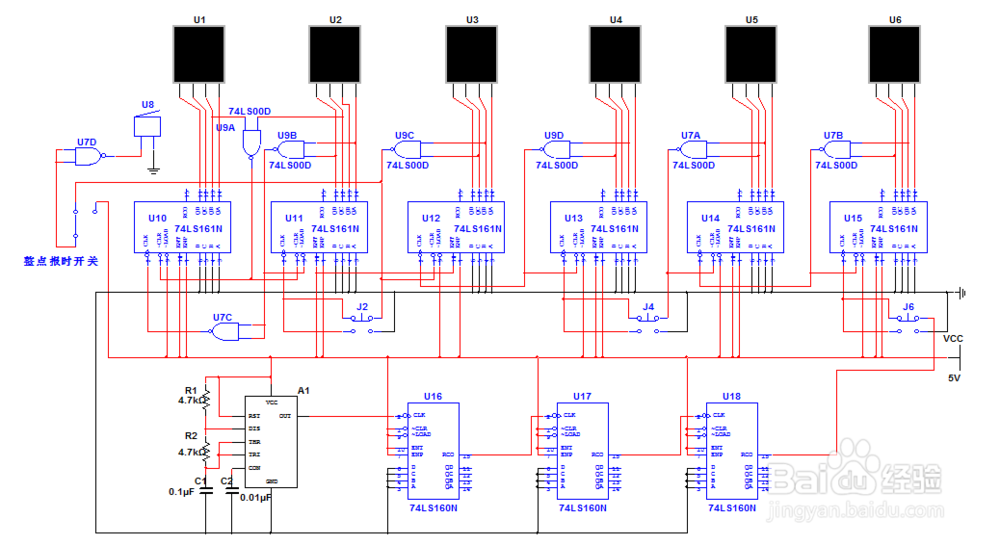

2、电路总设计图见下图所示。

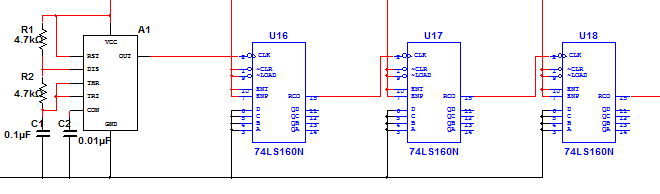

3、信号产生电路设计见下图,原理说明:利用555及电阻电容构成一个能够产生1kHz时钟信号的电路,再利用三个十进制的74LS160进行分频,从而产生1Hz的时钟信号。

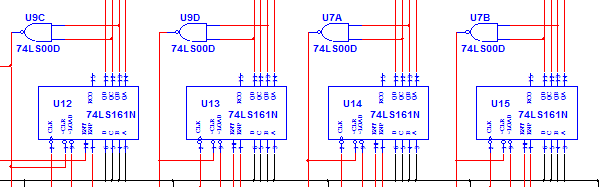

4、“秒”计数电路和“分”计数电路设计见下图,原理说明:利用十六进制的74LS161和与非门分别构成0-5循环计数器和0-9循环计数器,图中均利用的是清零法。

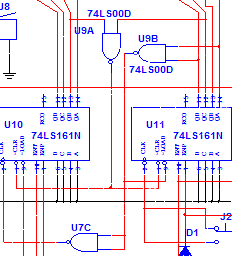

5、“时”计数电路设计见下图,原理说明:利用十六进制的74LS161和与非门构成一个0-9循环计数器并能够进位,但左右两计数器同时达到“2”和“4”时将它们同时清零,从而实现00-23循环计数的功能。

6、整点报时电路设计见下图,原理说明:利用蜂鸣器、与非门及开关实现,当“分”计数电路产生一个低平进位信号时,经过与非门变成高电平,从而使蜂鸣器发出响声,开关可以实现对该功能的控制。

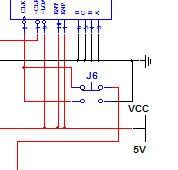

7、校时电路设计如下图,原理说明:利用一个按钮开关,当开关按下时,就会产生一个低电平给计数器,从而在下降沿时计数器加1。

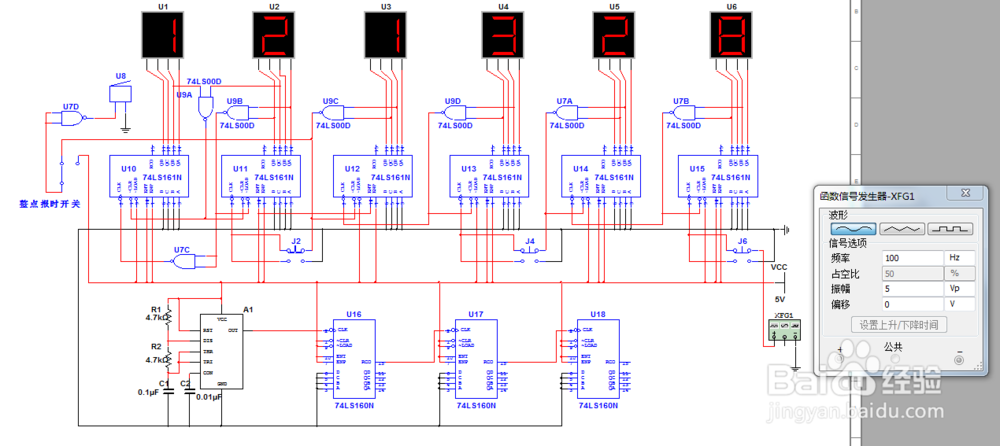

1、在Multisim软件里按设计方案及模块框图要求调出所需要的元件,然后连接电路图,结果如下图所示。

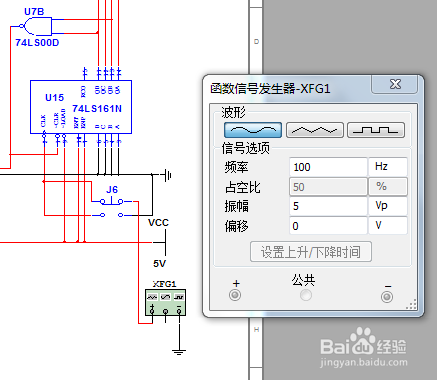

2、连好仿真电路图后,打开仿真开关,进行仿真。由于软件仿真很慢,要等很久数码管才会跳“1”。故用信号发生器,设置较高的频率并使其产生方波,如下图所示。从而能够更快的验证仿真结果,

3、结果如下图。结果显示数码管能够正常跳动并进位,当整点报时开关打开时,在达到整点是蜂鸣器响;当按下校时开关时,数码管会跳动加“1”。