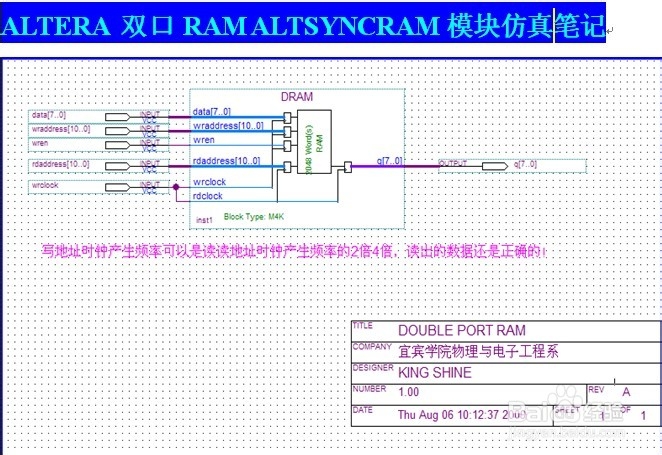

ALTERA 双口RAM ALTSYNCRAM模块仿真教程

一、

写地址时钟产生频率可以是读读地址时钟产生频率的2倍4倍,读出的数据还是正确的!

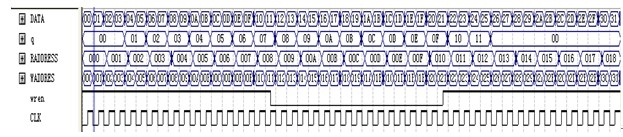

但是读写地址产生频率不能相同,否则就造成了同时对某一地址单元读写,就会没数据输出了。

如上图!

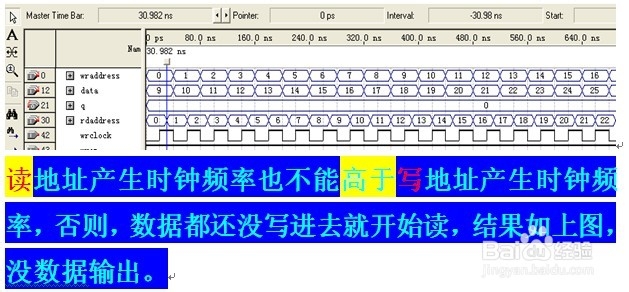

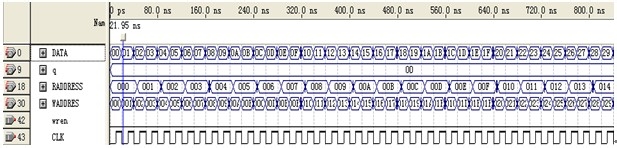

二、读地址产生时钟频率也不能高于写地址产生时钟频率,否则,数据都还没写进去就开始读,结果如上图,没数据输出。

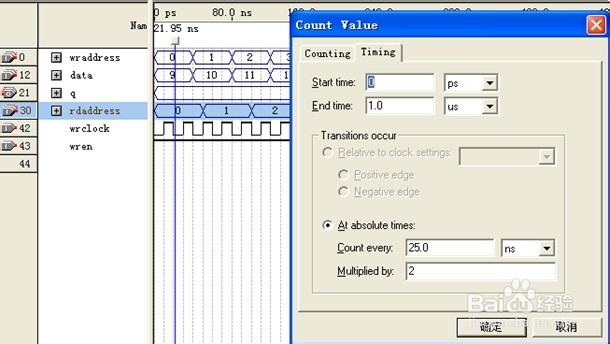

三、仿真设置

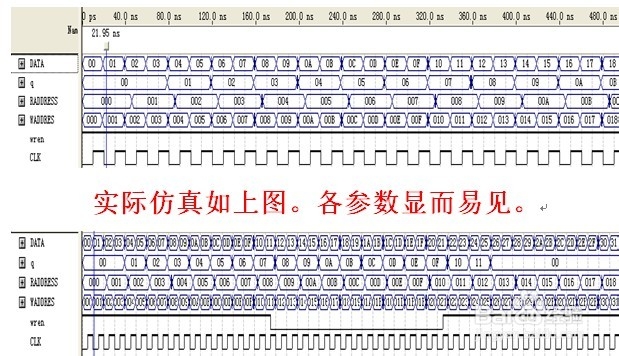

五、仿真结果

六、仿真中的注意事项及问题解决

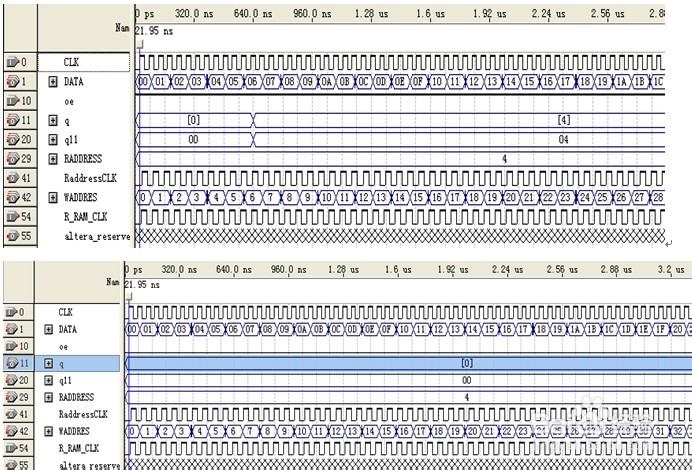

实际电路工作,CLK=20MHZ,2分频后作为读地址时钟,应该注意的是让RAM时钟和写地址的时钟保持一致。否则没有数据输出,或者是输出的数据丢失,主要是因为数据没有写入,也就是多时钟系统中的时钟紊乱问题。进去就开始读,结果如上图,没数据输出。

使能信号为低【0】的时候一段时间内仍然有数据输出,但是有时间延迟。时钟和写地址的时钟保持一致。否则没有数据输出,或者是输出的数据丢失,主要是因为数据没有写入,也就是多时钟系统中的时钟紊乱问题。

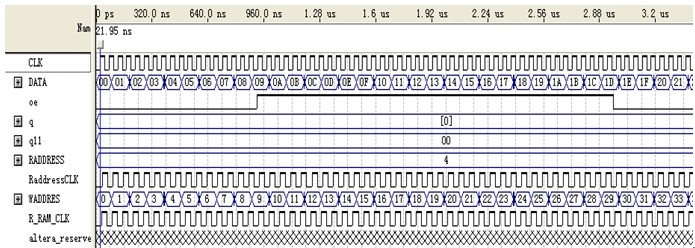

使能信号为低【0】的时候输出数据为零【0】

七、仿真电路原图

OE为0的时候如上图

OE为1的时候如上图

声明:本网站引用、摘录或转载内容仅供网站访问者交流或参考,不代表本站立场,如存在版权或非法内容,请联系站长删除,联系邮箱:site.kefu@qq.com。

阅读量:118

阅读量:98

阅读量:167

阅读量:83

阅读量:156